# LARGE LANGUAGE MODEL INFERENCE ACCELERATION: A COMPREHENSIVE HARDWARE PERSPECTIVE

Jinhao Li\*

Shanghai Jiao Tong University

Jiaming Xu

Shanghai Jiao Tong University & Infinigence-AI **Shan Huang**

Shanghai Jiao Tong University

Yonghua Chen

Infinigence-AI

Wen Li

Infinigence-AI

Jun Liu

Shanghai Jiao Tong University

Yaoxiu Lian

Shanghai Jiao Tong University

Jiayi Pan

Shanghai Jiao Tong University

Li Ding

Shanghai Jiao Tong University

Hao Zhou

Shanghai Jiao Tong University

Yu Wang Tsinghua University Guohao Dai<sup>†</sup>

Shanghai Jiao Tong University

& Infinigence-AI

## ABSTRACT

Large Language Models (LLMs) have demonstrated remarkable capabilities across various fields, from natural language understanding to text generation. Compared to non-generative LLMs like BERT and DeBERTa, generative LLMs like GPT series and Llama series are currently the main focus due to their superior algorithmic performance. The advancements in generative LLMs are closely intertwined with the development of hardware capabilities. Various hardware platforms exhibit distinct hardware characteristics, which can help improve LLM inference performance. Therefore, this paper comprehensively surveys efficient generative LLM inference on different hardware platforms. First, we provide an overview of the algorithm architecture of mainstream generative LLMs and delve into the inference process. Then, we summarize different optimization methods for different platforms such as CPU, GPU, FPGA, ASIC, and PIM/NDP, and provide inference results for generative LLMs. Furthermore, we perform a qualitative and quantitative comparison of inference performance with batch sizes 1 and 8 on different hardware platforms by considering hardware power consumption, absolute inference speed (tokens/s), and energy efficiency (tokens/J). We compare the performance of the same optimization methods across different hardware platforms, the performance across different hardware platforms, and the performance of different methods on the same hardware platform. This provides a systematic and comprehensive summary of existing inference acceleration work by integrating software optimization methods and hardware platforms, which can point to the future trends and potential developments of generative LLMs and hardware technology for edge-side scenarios. Our project is available at https://dai.sjtu.edu.cn/project.html.

Keywords Generative Large Language Model · Hardware · CPU · GPU · FPGA · ASIC · PIM · NDP

## 1 Introduction

Large Language Models (LLMs) have become cornerstones of modern artificial intelligence, demonstrating remarkable capabilities across a spectrum of fields, from natural language understanding to text generation [1, 2, 3, 4, 5]. LLMs

<sup>\*</sup>Email: kimholee@sjtu.edu.cn

<sup>&</sup>lt;sup>†</sup>Corresponding author: daiguohao@sjtu.edu.cn

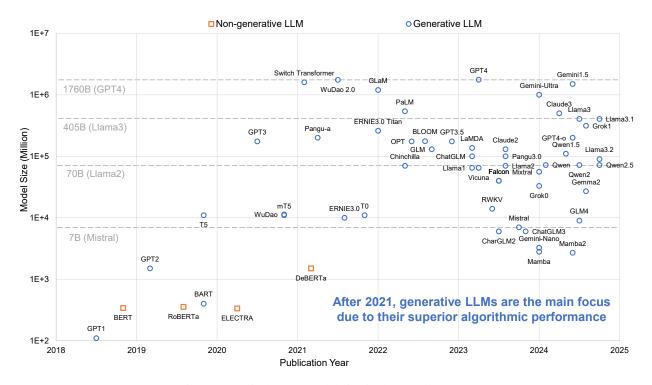

Figure 1: Typical LLM model size in the past six years.

can be categorized into two primary types: generative LLMs and non-generative LLMs. Non-generative LLMs, such as BERT [6], RoBERTa [7], ELECTRA [8], and DeBERTa [9], are designed to classify and make predictions based on input text. These models typically range in size from millions of parameters, allowing them to excel in tasks that require discernment and nuanced understanding. BERT, introduced in 2018, only has 340 million parameters. RoBERTa, introduced in 2019, slightly increases to 355 million parameters. And DeBERTa, released in 2021, increases to 1.5 billion. Generative LLMs, like GPT series [10, 11, 12, 13], T5 [14], OPT [15], BLOOM [16], and Llama series [17, 18, 19], have taken language generation to new heights. The model size increase of generative LLMs [10, 11, 20, 12, 14, 21, 22, 23, 24, 25, 26, 27, 28, 29, 15, 16, 30, 13, 31, 32, 33, 34, 35, 17, 18, 36, 37, 38, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 50, 19, 51, 52, 53, 54, 55, 56, 57] are particularly notable in the past 6 years, as shown in Figure 1. In 2018, GPT1 has only 110 million parameters, which grows to 1.5 billion in GPT2 in 2019. GPT3, launched in 2020, grows to 175B parameters dramatically, and GPT3.5 maintains the same size. After 2022, the model size maintains to several hundreds and thousands of billions like GPT4, Llama3, and Grok1 [58]. The evolution of LLMs has been characterized by an exponential growth in model parameters, which has been instrumental in enhancing their performance and versatility. Compared to non-generative LLMs, generative LLMs are currently the primary focus of research and development in the field of LLMs for their superior algorithmic performance. In recent years, after reaching the trillion-parameter scale in 2022, the parameter size of generative LLMs has stopped growing at an exponential rate. Two main reasons can explain this phenomenon: (1) As the amount of computation increases, the demand for computing power also rises significantly. The slow growth of hardware capabilities, particularly the slowing down of Moore's Law [59], limits the improvement of single-chip computing power. (2) Researchers have found that model performance is not solely dependent on the number of parameters, but also on the quantity and quality of training data [60]. By providing more qualified training tokens, the algorithmic performance can be further improved [18, 19]. At the same time, the parameter sizes of generative LLMs have shifted from "small to large" to "remaining stable" or even "shrinking". More models with fewer parameters are being released, particularly those that are better suited for deployment on edge devices. Notably, OpenAI's recent o1 [61] improves algorithm performance by introducing Chain-of-Thought (CoT) reasoning and multi-step inference. This new computational paradigm increases the importance of inference within the model, further highlighting the need to accelerate inference efficiency.

The advancements in generative LLMs are closely intertwined with the development of hardware capabilities. Due to the continuation of Moore's Law, from 2018 to 2022, GPU manufacturing processes have progressed from 12nm to 3nm, and the floating-point performance of single GPU die has increased from 130 TFLOPS to 989 TFLOPS. During model training, GPUs are used predominantly due to the user-friendliness of the CUDA programming stack [62] and the high scalability of GPU chips (*e.g.* NVLink [63]). During inference, various hardware options like CPU, GPU, FPGA, and

ASIC exhibit distinct hardware characteristics, which can help improving LLM inference performance. CPUs offer high programmability with a computing power of approximately 4 to 70 TOPS and with power consumption around from 4W to >200W. Modern CPUs (including some System-on-Chips, SoCs) enhance AI performance by integrating domainsspecific architecture (DSA) units. These include Apple's Neural Engine in the M2 Ultra [64], Qualcomm's NPU in the Snapdragon 8 Gen3 [65], and Intel's AVX/AMX ISA extensions [66]. GPUs excel in parallelism and computing power, delivering between  $\sim 70$  to > 1000 TOPS and featuring an impressive memory bandwidth of up to 1555 GB/s. On one hand, GPUs integrate a large number of SIMD cores and Tensor Cores in NVIDIA V100/A100/H100 [67, 68, 69] or Matrix Cores in AMD Instinct MI100/MI200/MI300 series [70, 71, 72] to enhance computing powers. On the other hand, GPUs support lower precision computations, such as INT8, FP8 and INT4 [68, 69], which allows for more multiplication units to be packed into a given chip area. Nevertheless, their power consumption is significantly higher, ranging from ~20W to >700W. FPGAs offer substantial parallelism and optimization capabilities, with computing performance between 50 to 100 TOPS. They are also more power-efficient, consuming about 75 to 100W. ASICs are often designed for specific applications and custom silicon designs, resulting in a wide range of computing power from GOPS to TOPS. Their power consumption can vary from the 0.1W range to several hundred watts. Due to their specialized design, ASICs generally offer higher computational efficiency and better energy efficiency compared to GPUs and CPUs. The unique attributes of each hardware type influence their optimal application in various inference scenarios.

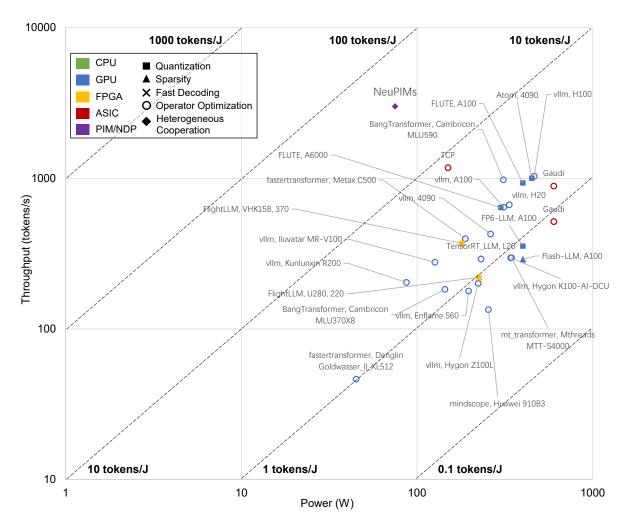

Here, we list and compare the existing surveys of LLM inference in Table 1. Previous surveys [73, 74, 75, 76, 77] primarily summarize various software optimization methods like quantization, sparsity, fast decoding for generative LLMs from an algorithm perspective. However, they do not take into account whether different optimization methods exhibit varying inference performance across different hardware platforms, and similarly, they also lack a fair and quantitative comparison. Surveys [78, 79] focus on accelerating transformer-based LLMs, including non-generative LLMs like BERT and a very small number of generative LLMs like GPT, but merely list the work done on different hardware platforms. They lack a summary and abstraction of the optimization methods used by different accelerators. Additionally, it only provides a relative comparison of speedup and energy efficiency with different baselines while lacking a fair comparison of inference performance, as what matters most for generative LLMs is the absolute inference speed (tokens per second, tokens/s) and inference energy efficiency (tokens per joule, tokens/J). Like [78, 79], surveys [80, 81] mainly focus on non-generative LLMs and one or two specific hardware platforms. Our survey focuses solely on generative LLMs, summarizing various software optimization methods in conjunction with multiple hardware platforms, including CPUs, GPUs, FPGAs, ASICs, and PIM/NDPs. For the first time, we innovatively use performance metrics that matter to generative LLMs: the number of tokens generated per second (tokens/s) and the number of tokens generated per joule (tokens/J). We compare (1) the performance of the same optimization methods across different hardware platforms, (2) the performance across different hardware platforms, and (3) the performance of different methods on the same hardware platform. This provides a systematic and comprehensive summary of existing inference acceleration work by integrating software optimization methods and hardware platforms.

Hardware Platforms Generative Software Quantitative Survey Optimization **CPU GPU FPGA** ASIC PIM/NDP Comparison LLM [73, 74, 75, 76, 77] [78, 79] 7 [80] X X X X X X [81] X J X X / ✓ X X Ours

Table 1: Comparison of existing LLM surveys

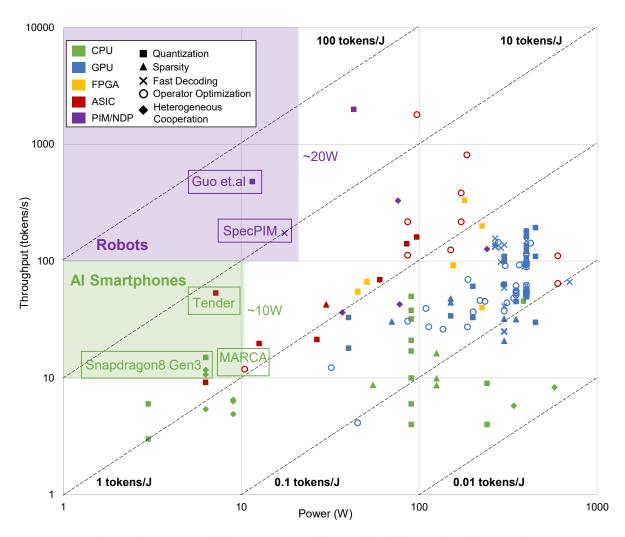

The article is meticulously structured to comprehensively summarize different optimizations on different hardware platforms for generative LLMs. Section 2 delves into the inference process of LLMs, providing an overview of the architecture and functioning of mainstream generative LLMs. Section 3 first summarizes the different optimization methods on various platforms such as CPU, GPU, FPGA, ASIC, and PIM/NDP in tabular form, and then provides a detailed description of each method and related works. Additionally, for each method, we also perform a qualified and quantitative comparison to show the difference among the hardware platforms. Furthermore, section 4 performs a qualitative and quantitative comparison of inference performance with batch sizes 1 and 8 on different hardware platforms. And we also point to the future trends and potential developments of generative LLMs and hardware technology for edge-side scenarios. Section 5 summarizes the work of this survey.

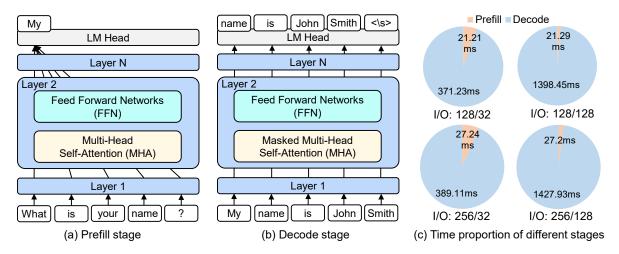

Figure 2: LLM inference includes prefill and decode stages. During inference in daily scenarios (input tokens:  $128 \le 1 \le 256$ , output tokens:  $0 \ge 32$ ), the time of decode stage is dominant.

## 2 Generative LLM Architecture

#### 2.1 Vanilla Generative LLM

The most common generative LLM is based on the transformer structure due to its abilities for capturing long-term dependencies [82]. The inference of generative LLM consists of two stages, the prefill stage and the decode stage, as shown in Figure 2. In the prefill stage, the input text is converted into embeddings and input into the LLM all at once. Each transformer layer performs operations, and the intermediate calculation results (K and V) are saved in the KV cache of the self-attention block for use in the decode stage. After completing calculating the last layer and LM head, the first token is generated. Then, in the decode stage, the LLM generates each token output autoregressively and updates the KV cache each time until generating the stop string. In the prefill stage, the attention computation has quadratical computational and storage complexity related with input text length. To address this limitation, many hardware-efficient LLMs focus on more efficient processing of longer length. For daily application scenarios where the number of input tokens is from 128 to 256 and output tokens larger than 32, we obtain that the time proportion of the decode stage exceeds 80% by profiling Llama2-7B on single NVIDIA A100 GPU, as shown in Figure 2 (c). Therefore, we summarize these LLMs in sub-section 2.2. And for the decode stage, we summarize hardware optimization methods for different platforms such as CPU, GPU, FPGA, ASIC, and PIM/NDP, and provide inference results for generative LLMs in latter sub-sections.

#### 2.2 Efficient Generative LLM

## 2.2.1 Transformer-based LLM

Transformer-XL [83] adopts a segment-level recurrence mechanism and a novel positional encoding scheme to learn dependencies beyond a fixed length without disrupting temporal coherence. Linear Transformer [84] represents selfattention as a linear dot product of kernel feature maps and alters the computation order by leveraging the associativity of matrix multiplication. This modification reduces the complexity from  $O(L^2)$  to O(L), where L is the context length, significantly accelerating the computation of autoregressive Transformers. Another efficient structure is the Attention-Free Transformer (AFT) [85]. Unlike vanilla transformers, which first compute the query-key product, AFT combines the key and value with a set of learned positional biases before performing element-wise multiplication with the query. As a result, the memory complexity of AFT is linear with respect to both the context size and feature dimensions, enabling support for larger input lengths and model sizes. Based on AFT, the Receptance Weighted Key Value (RWKV) [86] combines the efficient parallel training capabilities of Transformers with the efficient inference of RNNs. It leverages linear attention mechanisms and allows the model to be expressed as either a transformer or an RNN. It also enables parallel computation during training while maintaining constant computational and memory complexity during inference. DiJiang [87] introduces a novel frequency-domain kernelization method based on the Discrete Cosine Transform (DCT). It points out that improving attention mechanisms often requires extensive retraining, which is impractical for large language models with vast numbers of parameters. This approach enables the conversion of a pre-trained standard Transformer into a model with linear complexity and low training costs, utilizing a weighted

quasi-Monte Carlo method for sampling. Extensive experiments demonstrate that this method achieves performance comparable to the vanilla transformer while significantly reducing training costs and substantially increasing inference speed.

#### 2.2.2 SSM-based LLM

State Space Model (SSM) defines a linear mapping from an input x to output y through a hidden state h:

$$h = A \times h + B \times x$$

$$y = C \times h$$

(1)

where A is the state matrix, B is the input matrix, and C is the output matrix. In generative LLMs, SSM can understand and compress the input text into hidden states, and then generate output text based on these states. The Structured State Space Sequence Model (S4) [88] involves conditioning the matrix A with low-rank corrections, enabling it to be stably diagonalized, and simplifying the SSM to computations that involve an in-depth exploration of the Cauchy kernel. It offers significantly higher computational efficiency compared to previous methods while retaining its theoretical advantages. The Gated State Space Model (GSS) [89] is built on the effectiveness of gated activation functions. GSS demonstrates significantly faster training speeds on TPUs compared to S4, and it competes effectively with several Transformer-based LLMs. Hyena [90] addresses that existing sub-quadratic methods based on low-rank and sparse approximations need to be combined with dense attention layers to match the performance of transformers. Therefore, it introduces a sub-quadratic direct replacement for attention, constructed using interleaved implicit parameterized long convolutions and data-controlled gating. Hyena can improve accuracy by over 50 points compared to operators relying on state space models and other implicit and explicit methods. Due to the inability to perform content-based reasoning for linear attention, gated convolution, recurrent models, and S4, Mamba [43] makes the SSM parameters a function of the input and enables the model to selectively propagate or forget information along the sequence length dimension based on the current token. Additionally, a hardware-aware parallel algorithm was designed for the recurrent mode, enhancing computational efficiency. DenseSSM [91] enhance Mamba by selectively integrating shallow layer hidden states into deeper layers. Despite the dense connections, DenseSSM maintains both training parallelism and inference efficiency. Mamba2 [44] demonstrates that transformer and SSM model families are closely related through various decompositions of a well-studied class of structured quasi-separable matrices. Mamba2 also introduces the State Space Duality (SSD) framework, with its core layer being an improved version of the selective SSM used in Mamba and offering a  $2-8 \times$  speedup.

## 2.2.3 Hybrid LLM

Some other LLMs integrate transformer-based and SSM-based LLMs, leveraging the complete information extraction ability of attention and the information compression capability of SSM to enhance the performance for long inputs. The Block-State-Transformer (BST) [92] integrates an SSM sublayer for long-range contextualization with a block-transformer sublayer for short-term sequence representation. This architecture combines the strengths of SSMs and block attention, and explores three distinct, fully parallelizable variants. Griffin [93] combines gated linear recurrence with local attention, featuring the Hawk layer (a type of RNN with gated linear recurrence). Jamba [94] interleaves blocks of transformer and Mamba layers, harnessing the strengths of both model families. In some of these layers, mixture of expert (MoE) is added to increase model capacity while keeping the number of active parameters manageable. Unlike BST, Infini-Transformer [95] combines masked local attention and long-term linear attention within a single Transformer block. This Infini-Attention mechanism incorporates compressed memory into the original attention mechanism within the constraints of limited memory and computational resources. MEGALODON [96] is a neural architecture designed for efficient sequence modeling with infinite context length. It builds on the MEGA architecture (exponential moving average with gated attention) and introduces complex exponential moving average (CEMA), timestep normalization layer, normalized attention mechanism, and a pre-norm configuration with two-hop residuals to enhance its capability and stability.

## 3 Optimizations on Hardware Platforms

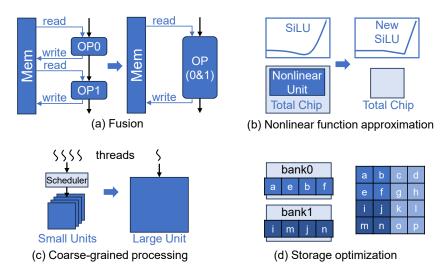

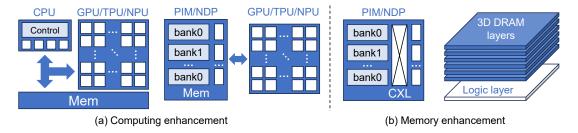

In this section, we provide an overview of the hardware platforms and various optimization techniques used in LLM inference. As shown in Table 2, the hardware platforms include CPU, GPU, FPGA, ASIC, and PIM/NDP, while the optimization methods include quantization, sparsity, fast decoding, operator optimization, heterogeneous cooperation, and homogeneous cooperation. In the following sections, we will provide a detailed explanation of the principles of each optimization method and related works, followed by a qualified and quantitative comparison.

Table 2: Existing generative LLM inference optimizations on different hardware platforms

| Shen et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Methods                    | CPU                                                                    | enerative LLM inference optimi                                                                                                                                                                                                                                                                                               |                                                                                            | ASIC                                                                                                                                     |                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T.MAC   [98]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                                                        |                                                                                                                                                                                                                                                                                                                              | FPGA                                                                                       |                                                                                                                                          | PIM/NDP                                                                                                                                                                                                   |

| Sparse   130 , ProSparse   131 , E-Sparse   135 , E-Spa | Quantization               | T-MAC [98],<br>Snapdragon<br>8 Gen3 [65],<br>Ilama.cpp [99],<br>NoMAD- | AWQ [102], SpQR [103],<br>SqueezeLLM [104], LLM-<br>MQ [105], APTQ [106], Li et<br>al. [107], LUT-GEMM [108],<br>FLUTE [109], FP6-<br>LLM [110], LLM.int8 [111],<br>SmoothQuant [112],<br>QUIK [113], Atom [114],                                                                                                            | HLSTrans-<br>form [117],<br>SECDA-<br>LLM [118],<br>Chen et al. [119],<br>FlightLLM [120], | MECLA [123],<br>OliVe [124], Li<br>et al. [125], Ten-                                                                                    | TransPIM [128],                                                                                                                                                                                           |

| decoding   [154], Looka-head   [155], Medusa   [156], EAGLE   [157, 158], Ouroboros   [159], Sequoia   [160], Draft&Verify   [161], Kangaro   [162], LayerSkip   [163], Adainfer   [164], RAEE   [165], MOD   [166]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | Sparse [130],                                                          | SparseGPT [133], Wanda [134], E-Sparse [135], Flash-LLM [136], Agarwalla et al. [137], DejaVu [138], Sparse Transformer [139], Bigbird [140], StreamingLLM [141], Longformer [142], Adaptively Sparse Attention [143], Reformer [144], Sparse Flash Attention [145], Sparse Sinkhorn Attention [146], H <sub>2</sub> O [147] |                                                                                            | TF-MVP [149],                                                                                                                            | HARDSEA [152],<br>Sharda et al. [129]                                                                                                                                                                     |

| FlashAttention   [169, 170], FlashDecoding   [171], FlashDecoding  |                            |                                                                        | decoding [154], Lookahead [155], Medusa [156], EAGLE [157, 158], Ouroboros [159], Sequoia [160], Draft&Verify [161], Kangaroo [162], LayerSkip [163], Adainfer [164], RAEE [165],                                                                                                                                            |                                                                                            | ~                                                                                                                                        | SpecPIM [168]                                                                                                                                                                                             |

| NeuPIMs [197],   NeuPIMs [197],   NeuPIMs [197],   NeuPIMs [198],   NonDE [199],   NonDE [199] |                            |                                                                        | FlashDecoding [171], FlashDecoding++ [172], Deep-Speed [173], vLLM [174], OpenPPL [175], cuBLAS [176], TensorRT-LLM [177], CUT-LASS [178], ByteTrans-                                                                                                                                                                        |                                                                                            | LPU [181], Con-<br>Smax [182],<br>MARCA [183],<br>TCP [184], Ha-<br>bana Gaudi [185],<br>Gaudi2 [186],<br>Gaudi3 [187],<br>Cerebras WSE- | tentionLego [190],<br>PIM-GPT [191],<br>SAL-PIM [192],                                                                                                                                                    |

| Homogeneous He et al. [210, DFX [212]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | PowerIn-<br>fer [195],<br>PowerInfer-                                  |                                                                                                                                                                                                                                                                                                                              |                                                                                            | 5 [100]                                                                                                                                  | IANUS [198], MoNDE [199], Sharda et al. [129], AttAcc [200, 201], Kang et al. [202], Kim et al. [203], H3D- Transformer [204], CXL-PNM [205], 3D-HI [206], SK Hynix AiMX/AiMX- xPU [207, 208], Cambricon- |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Homogeneous<br>Cooperation | He et al. [210, 211]                                                   |                                                                                                                                                                                                                                                                                                                              | DFX [212]                                                                                  |                                                                                                                                          | F 47.3                                                                                                                                                                                                    |

## 3.1 Quantization

#### 3.1.1 Overview

Quantization converts the model's weights and activations from high-precision formats (32-bit floating-point numbers) to low-precision formats (such as 4-bit integers). This process aims to reduce the model's storage requirements and computational costs while maintaining its accuracy. From the perspective of data format, quantization includes uniform and non-uniform quantization. Uniform quantization is a method where the value range is divided into several equal intervals. In uniform quantization, the entire range of values is partitioned into equally sized intervals, with each interval mapped to a discrete representation value. These discrete values are typically represented using fewer bits (e.g., 8 bits). The advantages of uniform quantization include its simplicity and high computational efficiency. However, it may not effectively capture the data distribution characteristics, especially when the data distribution is uneven, potentially leading to significant information loss. Non-uniform quantization, on the other hand, uses intervals of varying sizes based on the actual data distribution. It divides the data range into different-sized intervals, for example, using smaller intervals in regions where the data distribution is dense and larger intervals where the distribution is sparse. This approach can better preserve the details and features of the data, thus improving the model's accuracy. Non-uniform quantization typically requires additional computation and storage to manage the quantization intervals, but it provides higher precision and effectiveness in quantization.

Granularity in quantization is crucial for determining model performance and efficiency. The granularity are group-wise, channel-wise, and tensor-wise. Group-wise granularity is a coarser approach where multiple channels or layers are quantized with the same parameters. This means that within a group, all channels or layers use identical quantization settings. The advantage of group-level granularity is its simplicity and relatively low computational and storage overhead. However, it may not capture the individual characteristics of each channel or layer as effectively, potentially resulting in some compromise in model performance. Channel-wise granularity involves quantizing each channel individually within the model. Each channel can have its own quantization parameters, allowing for more precise adjustments according to the weight distribution and activation characteristics of each channel. This granularity offers a balance between precision and flexibility, though it increases the complexity of implementation and computation. Tensor-wise granularity is the most detailed approach, where each tensor (such as weight tensors or activation tensors) is quantized separately. This means that each tensor has its own quantization parameters, enabling the highest degree of adaptation to the specific characteristics of each tensor and providing the best precision. However, this level of granularity comes with the highest computational and storage costs and is the most complex to implement. There are two main quantization methods: weight-only quantization and weight-activation quantization.

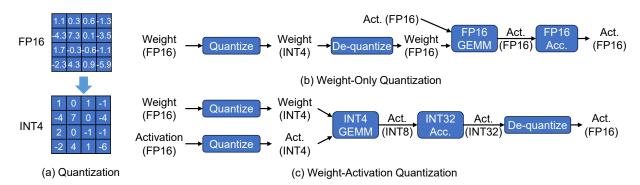

Figure 3: Two main quantization methods: weight-only quantization and weight-activation quantization.

Weight-Only Quantization. Weight-only quantization involves converting the model's weight parameters from high-precision formats (like 32-bit floating-point numbers) to low-precision formats (such as 8-bit integers). This process typically includes discretizing the weights by mapping them to a finite set of discrete values and then representing these values with fewer bits (e.g., 8 bits). This approach significantly reduces storage requirements and accelerates computation. Weight-only quantization can be implemented using methods such as uniform quantization, which divides the weight range into equal intervals, or non-uniform quantization, which adjusts the intervals based on the distribution of weights to better preserve model accuracy. Matrix decomposition quantization is a specialized method where a large matrix is approximated by the product of several smaller matrices. This technique reduces the computational and storage requirements by representing a large matrix with multiple smaller matrices, which can be stored and processed in lower precision formats. This method is particularly beneficial for managing extremely large models, as it helps lower computational complexity and storage overhead.

**Weight-Activation Quantization.** Weight-activation quantization extends the concept of weight-only quantization to include the activations generated during model inference. In this method, both the weights and the activations at each layer are quantized to lower precision formats. This reduces memory bandwidth requirements and enhances inference speed. The challenge with weight-activation quantization is to manage the trade-off between quantization errors and model accuracy. Techniques such as dynamic range quantization or specific quantization schemes are used to balance precision and computational efficiency. Table 3 shows the usage of two quantization methods across different hardware platforms.

| Hardware | Weight-Only Quantization | Weight-Activation Quantization |

|----------|--------------------------|--------------------------------|

| CPU      | <b>✓</b>                 | X                              |

| GPU      | <b>✓</b>                 | ✓                              |

| FPGA     | ×                        | <b>√</b>                       |

| ASIC     | ×                        | ✓                              |

| PIM/NDP  | Х                        | ✓                              |

Table 3: Quantization on CPU, GPU, FPGA, ASIC, and PIM/NDP

## 3.1.2 CPU

Weight-Only Quantization. The optimization methods of quantization on CPUs mainly focus on weight-only quantization. Shen et al. [97] leverage Intel Neural Compressor to automate the INT4 quantization process with negligible accuracy loss, supporting various quantization recipes such as GPTQ [101], AWQ [102] and TEQ [213]. They further develop a tensor library tailored for CPUs, which supports mainstream instruction sets like AVX2, AVX512, AVX512\_VNNI, and AMX. By providing INT4 dequantization kernels on x86 CPUs, the experimental results on mainstream LLMs including Llama2, Llama and GPT-NeoX shows the latency of token generation is ranging from 12.5 tokens/s to 50 tokens/s for models with parameters ranging from 6B to 20B, by using a single socket of 4th Generation Intel Xeon Scalable Processors [66]. Qualcomm Snapdragon 8 Gen3 SoC [65] utilizes its proprietary Hexagon 700 AI processor and quantization techniques to support the efficient LLM execution. For Llama2-7B with 4-bit quantization, it achieves about 15 tokens/s. Some open-source repositories like llama.cpp [99] are designed for efficient LLM inference across diverse hardware platforms including CPUs, GPUs and ASICs. For Llama2-7B with 4-bit quantization, llama.cpp achieves 6 tokens/s with a single core and 32 tokens/s with eight cores on Apple M2-Ultra processors. For Llama2-7B with 2-bit quantization, llama.cpp achieves 4 tokens/s with a single core and 21 tokens/s with eight cores on M2-Ultra.

Due to the overheads of weight dequantization from integer to floating, T-MAC [98] leverages lookup tables (LUTs) for efficient low-bit LLM inference on edge CPUs, circumventing the need for dequantization and mixed precision matrix multiplication. For Llama2-7B with 4-bit quantization, T-MAC achieves 10 tokens/s with a single core and 38 tokens/s with eight cores on Apple M2-Ultra processors [64], and 3 tokens/s on Raspberry Pi 5 [214] integrated with ARM Cortex-A76. For Llama2-7B with 2-bit quantization, T-MAC achieves 17 tokens/s with a single core and 50 tokens/s with eight cores on M2-Ultra, and 6 tokens/s on Raspberry Pi 5. Furthermore, due to the vast quantities of expensive Multiply-Add (MAD) matrix operations in the attention computations, NoMAD-Attention [100] design an efficient attention algorithm that replaces MAD operations with in-register lookups. Through hardware-aware algorithmic designs, NoMAD-Attention achieves the computation of attention scores using repeated fast accesses to SIMD registers despite their highly limited sizes. Empirical evaluations demonstrate that for CodeLlama-7B with 4-bit quantization, NoMAD-Attention achieves 9 tokens/s with short context (e.g. 128) and 4 tokens/s with long context (e.g. 16k) on 2 Intel Xeon E5-2695 V3 14-core CPUs.

## 3.1.3 GPU

Weight-Only Quantization. GPTQ [101] is an one-shot weight quantization method based on approximate second-order information and error compensation, that is both highly-accurate and highly-efficient. It can quantize GPT models with 175 billion parameters in approximately four GPU hours, reducing the bitwidth down to 3-bit or 4-bit per weight, with negligible accuracy degradation relative to the uncompressed baseline. Experimental results show that the average time of per token of 3-bit OPT-175B model obtained via GPTQ running on a single A100 (80GB) is 14.1 tokens/s, which is about 3.25× faster than the FP16 version (running on 5 GPUs). On more accessible GPUs, such as the NVIDIA A6000 (48GB), the average time of per token is 7.7 tokens/s (running on 2 GPUs), which is about 4.53× faster than the FP16 version (running on 8 GPUs). AWQ [102] is based on the observation that protecting 1% of salient weights whose activations are extremely large can greatly reduce quantization error. It first searches for the optimal per-channel scaling and then multiplies the salient weights with the per-channel scalings. It also reduces the bitwidth down to 3 or 4 bits per weight. Experimental results with INT4 implementation show that for Llama-2-7B, it improves the inference speed from 52 tokens/s to 194 tokens/s on RTX 4090 desktop GPU (3.73× speedup). For Llama-2-13B, the inference

speed is 110 tokens/s on RTX 4090 desktop GPU. On the laptop RTX 4070 GPU (8GB), it is able to run Llama-2-13B models at 33 tokens/s, while the FP16 implementation cannot fit 7B models.

To further reduce the accuracy loss for smaller models in the 1-10B parameter range, SpOR [103] works by identifying and isolating outlier weights, which cause particularly-large quantization errors, and storing them in higher precision like half data type (16-bit), while compressing all other weights to 3-4 bits, and achieves relative accuracy losses of less than 1% in perplexity for highly-accurate LLaMA and Falcon LLMs. Experimental results show that SpQR with 3-bit and 16-bit quantization achieves 57 tokens/s, 44 tokens/s, 22 tokens/s and 12 tokens/s on A100 GPU, respectively. Unlike SpQR, SqueezeLLM [104] proposes a sensitivity-based non-uniform quantization method, which searches for the optimal bit precision assignment based on second-order information. It also applies dense and sparse decomposition that stores outliers and sensitive weight values in an efficient sparse format. Experimental results show that SqueezeLLM with 3bit and 16-bit quantization achieves 63.5 tokens/s, 49.2 tokens/s, 29.1 tokens/s and 14.5 tokens/s on A6000 GPU, respectively. LLM-MQ [105] proposes sensitivity-based precision allocation to assign the proper bitwidth for each layer within the given budget for weight memory based on their first-order information and quantization error. It also develops an efficient CUDA core kernels to accelerate LLMs by fusing the dequantization and general matrix-vector multiplication (GEMV). LLM-MQ deploys INT4 quantized Llama2-7B model on NVIDIA T4 GPU achieves up to 1.6× end-to-end speedup compared to the pytorch FP16 baseline. APTQ [106] proposes an attention-aware 2/4-bit mixed-precision quantization for LLMs, which considers not only the second-order information of each layer's weights, but also, for the first time, the nonlinear effect of attention outputs on the entire model. Li et al. [107] are the first to propose an intra-weight mixed-precision quantization for LLMs to further reduce accuracy loss under 3-bit. By applying 2/4-bit mixed-precision quantization with memory alignment and exclusive 2-bit sparse outlier reservation with minimum speed degradation, it achieves 2.91-bit for each weight considering all scales/zeros for different models with negligible loss. Additionally, they design an asynchronous dequantization and fuse the dequantization and GEMV kernels during inference. For Llama2-7B, it achieves 45.2 tokens/s on RTX 3090 GPU and 34.0 tokens/s on RTX 2080 GPU.

LUT-GEMM [108] proposes an efficient LUT-based GPU kernel for quantized matrix multiplication, which not only eliminates the resource-intensive dequantization process but also reduces computational costs compared to previous kernels for weight-only quantization. The impact of LUT-GEMM is facilitated by implementing high compression ratios through low-bit quantization and efficient LUT-based operations. For Llama-7B with 4-bit quantization, it achieves 163.9 tokens/s on A100 GPU, achieving a remarkable 1.64× token generation latency improvement compared to the pytorch FP16 baseline. FLUTE [109] is a flexible lookup table engine for LUT-quantized LLMs, which uses offline restructuring of the quantized weight matrix to minimize bit manipulations associated with unpacking, and vectorization and duplication of the lookup table to mitigate shared memory bandwidth constraints. For Llama3-8B with 4-bit quantization, it achieves 91.3-99.8 tokens/s and 113.7-121.7 tokens/s on NVIDIA A6000 and A100 GPUs, respectively. For Llama3-8B with 3-bit quantization, it achieves 91.9-110.0 tokens/s and 117.7-135.5 tokens/s on NVIDIA A6000 and A100 GPUs, respectively.

To effectively reduce the size of LLMs and preserve the model accuracy, FP6-LLM [110] proposes FP6 quantization on GPUs with TC-FPx, the first full-stack GPU kernel design scheme with unified Tensor Core support of float-point weights for various quantization bit-width. It solves the unfriendly memory access of model weights with irregular bit-width and high runtime overhead of weight de-quantization. Experimental results shows that for Llama2-13B with FP6 quantization, it achieves about 55 tokens/s on NVIDIA A100 GPU.

Weight-Activation Quantization. In addition to hardware units that support FP16 computations, NVIDIA GPUs also provide hardware units that support INT4, INT8, and FP8 computations. The number of these computation units can be 2× and 4× greater than FP16 on each chip. Compared to weight-only quantization, weight-activation quantization can utilize INT4, INT8, and FP8 computations, thereby maximizing the peak computational performance of the GPU. Since the prefill phase in LLM inference is compute-bound, weight-activation quantization can significantly enhance performance during this stage. LLM.int8 [111] uses vector-wise quantization with separate normalization constants for each inner product in the matrix multiplication, to quantize most of the features. For the outliers, it isolates the outlier feature dimensions into a 16-bit matrix multiplication while still more than 99.9% of values are multiplied in 8-bit. For BLOOM-176B model, LLM.int8 achieves 4.05 tokens/s, 30.3 tokens/s and 109.77 tokens/s for batch size 1, 8 and 32, respectively, on 3 A100 GPUs in decode phase. The inference speed is slightly slower but close to 16-bit inference with less GPU consumption. SmoothQuant [112] enables 8-bit weight and 8-bit activation (W8A8) quantization for LLMs. Based on the fact that weights are easy to quantize while activations are not, SmoothQuant smooths the activation outliers by offline migrating the quantization difficulty from activations to weights with a mathematically equivalent transformation. SmoothQuant enables an INT8 quantization of both weights and activations for all the matrix multiplications in LLMs. SmoothQuant achieves up to 1.56× speedup and 2× memory reduction for LLMs with negligible loss in accuracy. QUIK [113] is for the first time, that the majority of inference computations for LLMs can be performed with both weights and activations being cast to 4 bits. QUIK compresses most of the

weights and activations to 4-bit, while keeping some outlier weights and activations in higher-precision. It also provides GPU kernels matching the QUIK format with highly-efficient layer-wise runtimes, which lead to practical end-to-end throughput improvements of up to  $3.4 \times$  relative to FP16 execution in prefill phase.

Prevalent quantization schemes (e.g., W8A8) cannot fully leverage the capabilities of modern GPUs, such as 4-bit integer operators, resulting in sub-optimal performance. To maximize the throughput, Atom [114] significantly boosts serving throughput by using low-bit operators and considerably reduces memory consumption via low-bit quantization. It attains high accuracy by applying a novel mixed-precision and fine-grained quantization process. For single batch inference, Atom can achieve about 30 tokens/s for on a NVIDIA RTX 4090 GPU. Atom improves end-to-end throughput by up to  $7.73\times$  compared to the FP16 and by  $2.53\times$  compared to INT8 quantization, while maintaining the same latency target.

Compared to integer quantization, floating-point (FP) quantization can better handle long-tail or bell-shaped distributions, and it has emerged as a default choice in many hardware platforms. LLM-FP4 [115] quantizes both weights and activations in LLMs down to 4-bit floating-point values (W4A4) with negligible accuracy loss. Due to the lack of PF4 computing unit in GPUs, its decoding speed maybe slower than FP16 baseline.

#### 3.1.4 FPGA

Weight-Activation Quantization. FlexRun [116] uses 8-bit quantization (W8A8), conducts an in-depth design space exploration to find the best accelerator architecture for a target LLM model, and automatically reconfigures the accelerator based on the exploration results. With the implementation on Intel Stratix 10 GX and MX FPGAs, FlexRun outperforms the current state-of-the-art FPGA-based accelerator by  $1.15 \times -1.50 \times$  for GPT2, respectively. Compared to Nvidia's V100 GPU, FlexRun achieves 2.69× higher performance on average for various GPT2 models. HLSTransform [117] uses HLS to design a FPGA accelerator and synthesis combined with pipelining, memory unrolling, and memory partitioning and transfer optimizations, with the addition of 8-bit integer quantization (W8A8). On a tiny model with 110 million parameters, HLSTransform achieves 57.11 tokens/s on Xilinx Virtex UltraScale+ VU9P FPGA. SECDA-LLM [118] utilizes quantization (W3A8) and designs an efficient FPGA-based LLM accelerators for the llama.cpp inference framework. By deploying on the PYNQ-Z1 board, it achieves 0.588 tokens/s for the TinyLlama model (1.1B). Chen et al. [119] investigate the feasibility and potential of model-speciic spatial acceleration for LLM inference on FPGAs. They introduce a comprehensive analytical model to estimate the LLM inference performance of FPGA accelerator with W4A8 quantization, and provide a library of high-level synthesis (HLS) kernels that are composable and reusable. For Llama2-7B, during prefilling phase, they can achieve about 213 tokens/s, 43 tokens/s, and 320 tokens/s on Xilinx Alveo U280, VCK5000, and VHK158 FPGAs, respectively. During decode stage, they can achieves about 200 tokens/s, 40 tokens/s, and 333 tokens/s on Xilinx Alveo U280, VCK5000, and VHK158 FPGAs, respectively.

## 3.1.5 ASIC

Weight-Only Quantization. Despite the memory footprint reduction achieved by weight-only quantization, the actual computing performance is not really improved due to dequantization from integer to float. FIGNA [122] proposes dedicated FP-INT arithmetic units designed specifically for FP-INT MAC operations and integrates them on the accelerator. FIGNA with FP16-INT4 provides 3.2768 TOPS computing power and 26.58W power consumption by considering all memory access in 28nm at 100MHz. Estimated result shows that for OPT-6.7B it can achieve 21.332 tokens/s in decode stage. Different from normal quantization methods, MECLA [123] proposes a parameter-efficient scaling sub-matrix partition method (SSMP) to decompose large weight matrices into several tiny-scale source sub-matrices (SS) and derived sub-matrices (DS). For memory issues, SSMP avoids accessing the full weight matrix but only requires small SS and DS scaling scalars. For computation issues, the proposed accelerator fully exploits the intermediate data reuse of matrix multiplication via on-chip matrix regrouping, inner-product multiplication reassociation, and outer-product partial sum reuse. Totally, it can reduce 83.6% memory access and 72.2% computation. MECLA provides 14.008 TOPS computing power and ~96W (1.9763W+94W) power consumption by considering all memory access under 28nm. For Llama2-7B and BLOOM-7B, compared to NVIDIA V100 GPU, MECLA achieves 6.74× and 5.91× inference speedup (~161 tokens/s and 141 tokens/s, respectively).

**Weight-Activation Quantization.** Based on the key insight that outliers are important while the normal values next to them are not, OliVe [124] adopts an outlier-victim pair (OVP) quantization and handles outlier values locally with low hardware overheads. This enables a memory-aligned W4A4/W8A8 quantization, which can be efficiently integrated to the existing hardware accelerators like systolic array and tensor core. OliVe provides 0.71 TOPS computing power and  $\sim$ 8W (0.2806W+7.9872W) power consumption by considering all memory access under 22nm. Estimated results shows that for OPT-6.7B it can achieve 9.173 tokens/s in decode stage. Li et al. [125] uniformly group weights and activations to ensure workload balance for hardware, and propose two approaches called channel sorting and channel selection to

enhance the performance of quantization. It provides 1.43 TOPS computing power and  $\sim$ 8.5W (0.472W+7.9872W) power consumption by considering all memory access under 65nm. Estimated results shows that for OPT-6.7B it can achieve 19.733 tokens/s in decode stage. Tender [126] decomposes weight and activation matrices by groups with different size to smooth the impact of outliers. And the format of scale factors are powers of two apart, which avoids explicit dequantization and extension to the commodity tensor compute hardware. It is 7.174W (1.60W+5.574W) power consumption by considering HBM2 memory access under 28nm. Result shows that for OPT-6.7B, Tender achieves  $1.33 \times$  speedup (53.33 tokens/s) than NVIDIA A100 GPU.

#### 3.1.6 PIM/NDP

ReRAM-based analog PIM architectures perform integer MVMs using voltage, current, and conductance in the analog domain, limiting their application to the more accurate floating point (FP) data format. Guo et al. [127] propose an ReRAM and 3D-SRAM-based hybrid PIM architecture with non-uniform data format, achieving FP-based algorithm accuracy, high device utilization, and high energy efficiency. At the software level, they first analyze the impact of quantization errors on the accuracy of attention-free LLMs. For the quantization error-insensitive MVM operations, they propose the PIM-oriented exponent-free non-uniform (PN) data format. The proposed PN format can be flexibly adjusted to fit the data distribution and approach the accuracy of the FP format using bit-slicing-based full INT operations. For the quantization error-sensitive EWM operations, they introduce the multiplication free approximated FP multiplications to reduce the additional hardware overhead for PIM. At the hardware level, they propose a hybrid PIM architecture, including an ReRAM analog PIM using shift-and-add for PN-based MVMs, and a 3D-SRAM digital PIM with high utilization for multiplication-free FP-based element-wise operations. Extensive experiments show that the proposed PIM architecture achieves up to  $89 \times$  and  $16 \times$  speedup with  $2537 \times$  and  $12 \times$  energy efficiency improvement compared with GPU and PIM-baseline, respectively. TransPIM [128] is a memory-based acceleration for Transformer using software and hardware co-design. In the software-level, TransPIM adopts a token-based dataflow to avoid the expensive inter-layer data movements introduced by previous layer-based dataflow. In the hardware-level, TransPIM introduces lightweight modifications in the conventional HBM architecture to support PIM-NMC hybrid processing and efficient data communication for accelerating Transformer-based models. TransPIM system uses the 8GB HBM as the memory with  $2.15mm^2$  area overhead and about 40.01W power consumption. Experimental results show that for GPT2 models, TransPIM achieves at least 22.1× speedup than NVIDIA RTX 2080Ti GPU. Other PIM/NDP accelerators like TransPIM [128] and Sharda's method [129] also involve the quantization to further improve LLM inference.

#### 3.1.7 Quantitative Comparison

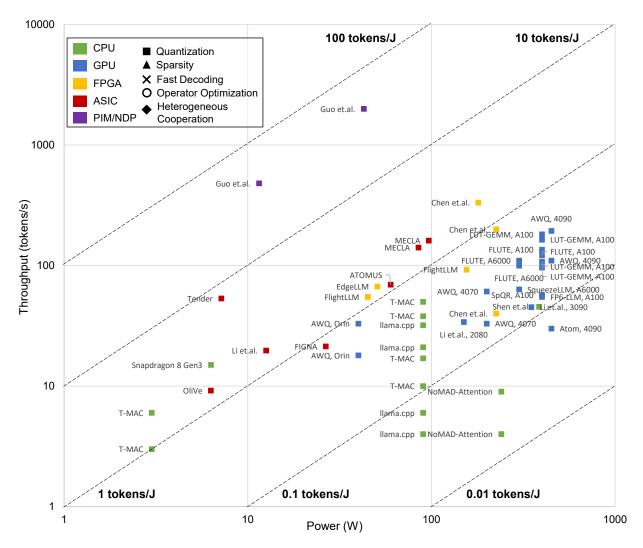

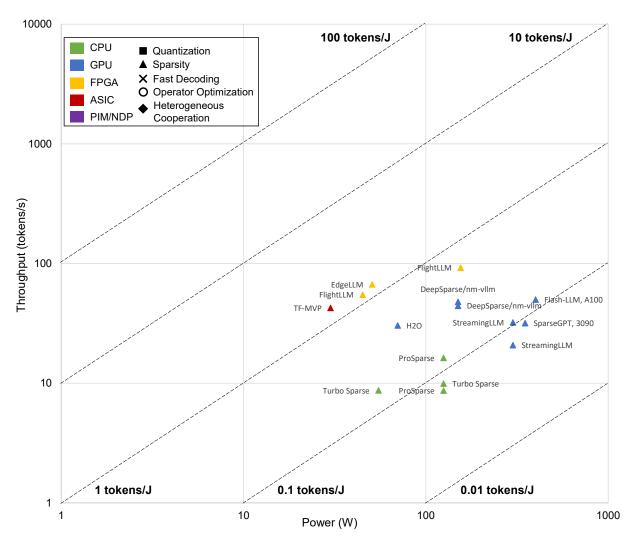

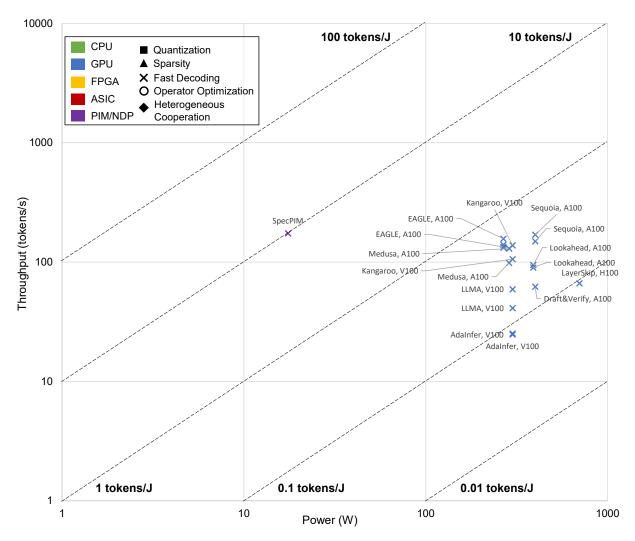

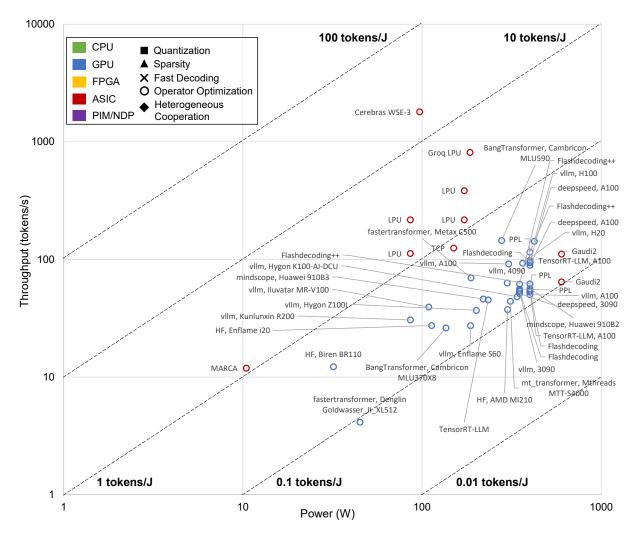

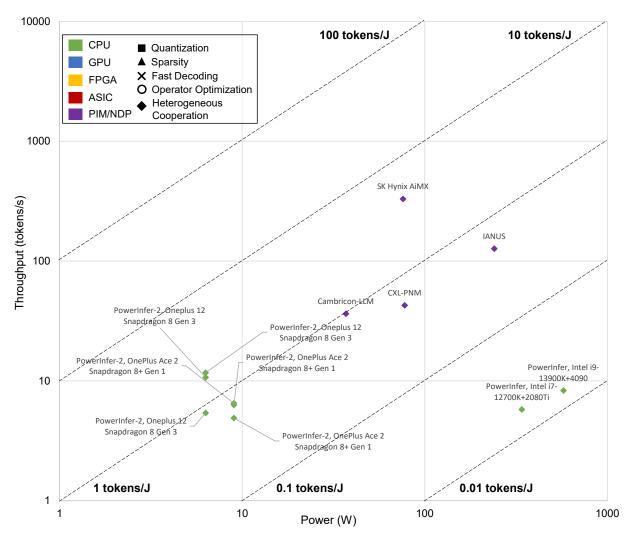

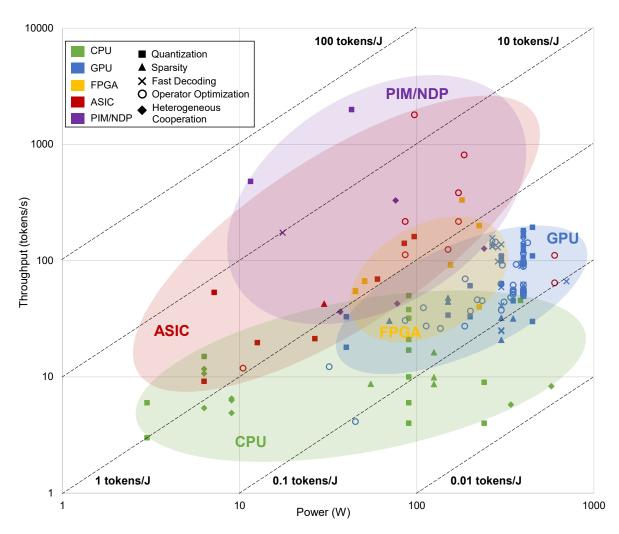

We first compare the power consumption, inference speed and energy efficiency for different hardware platforms, in Figure 4. For quantization, power consumption ranges from 3W to 450W, with inference speeds between 3 tokens/s and 1998 tokens/s. The energy efficiency ranges from 0.0167 tokens/J to 46.66 tokens/J. T-MAC [98] (CPU) achieves the lowest power consumption with 3W and Guo et al. [127] (PIM/NDP) achieves the highest throughput with batch size 1 (pre-silicon simulation result). And Guo et al. [127] also achieves the highest energy efficiency with 46.66 tokens/J.

- For CPUs, power consumption ranges from 3W to 385W, with inference speeds between 3 tokens/s and 50 tokens/s, located in the bottom part of the figure. The energy efficiency ranges from 0.0167 tokens/J to 2.38 token/J. Additionally, we observe edge CPUs (including CPU SoCs) with 3W to 6W power consumption exhibit higher energy efficiency (0.544 tokens/J to 2.38 tokens/J).

- For GPUs, power consumption ranges from 40W to 450W, with inference speeds between 18 tokens/s and 194 tokens/s, situated in the upper right part of the figure. The energy efficiency ranges from 0.0667 tokens/J to 0.825 token/J. Compared to other hardware, GPUs can achieve higher absolute inference speeds due to their high computing power and high bandwidth. When quantization methods are used, the memory access bottlenecks in LLM inference are alleviated, further unlocking computing power.

- For FPGAs, power consumption ranges from 45W to 225W, with inference speeds between 40 tokens/s and 333 tokens/s, also in the upper right part of the figure. The energy efficiency ranges from over 0.178 tokens/J to 1.85 tokens/J, which is higher than GPUs and server CPUs.

- For ASICs, power consumption ranges from 6.3W to 96.66W, with inference speeds between 9.173 tokens/s and 161.086 tokens/s, found in the upper left section of the figure. The energy efficiency ranges from 0.803 tokens/J to over 7.434 tokens/J, outperforming CPU, GPU and FPGA hardware platforms.

- For PIM/NDPs, power consumption ranges from 11.516W to 42.819W, with inference speeds between 481 tokens/s and 1998 tokens/s, found in the upper left section of the graph. The energy efficiency outperforms other hardware platforms.

Figure 4: LLM ( $\sim$  7 billion parameters) decode stage throughput (batch size 1) vs power on different platforms with quantization.

Overall, both weight-only quantization and weight-activation quantization methods can enhance absolute inference speed and improve energy efficiency. Weight-only quantization reduces bandwidth requirements but introduces additional dequantization operations, which can increase hardware power consumption while improving absolute speed. On the other hand, weight-activation quantization reduces the hardware compute unit area and power consumption by using smaller-width computation units, leading to improved absolute speed while lowering overall hardware power consumption.

#### 3.2 Sparsity

## 3.2.1 Overview

Sparsity reduces the number of non-zero elements and skip the multiplication and addition with zero to improve efficiency of computation and storage. Due to the presence of attention computations in standard transformer-based large models, sparsification methods include not only weight sparsity and activation sparsity but also attention sparsity. Weight sparsity is primarily achieved through pruning methods, including global pruning, layer-wise pruning, and structured pruning, which reduce the size of weight matrices and leverage sparse matrix libraries for optimization. Activation sparsity focuses on reducing the computation of activation values by employing techniques such as activation pruning (e.g., threshold pruning) and dynamic sparsity, with hardware optimizations utilizing sparse data structures to enhance efficiency. Attention sparsity addresses the optimization of computations in self-attention mechanisms,

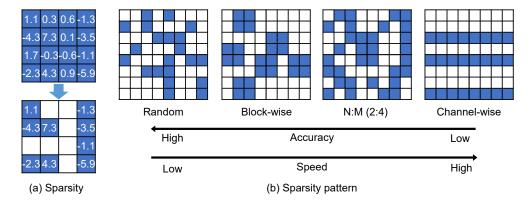

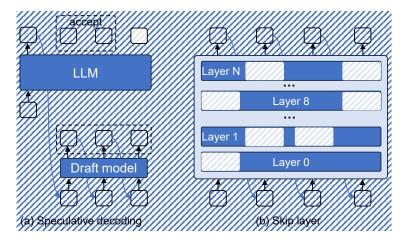

Figure 5: Sparsity and sparsity patterns.

employing methods like local attention, block-wise attention, and sparse attention matrices, which reduce computational load by limiting the calculation scope or using sparse matrix storage. These sparsity strategies help improve model inference efficiency, particularly when dealing with large-scale data and complex tasks.

Sparsity patterns can be categorized into random and structured sparsity as shown in Figure 5. **Random pattern** involves a random distribution of zero elements within the matrix, achieving higher accuracy but potentially lower speed for computation. **Structured pattern** applies a specific pattern to the sparsity, improving computational efficiency by aligning with hardware optimizations. Within structured sparsity, common patterns include block-wise sparsity, N:M sparsity, channel-wise sparsity and some combinations of structured pattern sparsity. These structured patterns offer predictable and optimized computational benefits. Block-wise sparsity involves dividing the weight matrix into smaller blocks and applying sparsity within each block. N:M sparsity retains M non-zero elements out of every N elements, improving efficiency through hardware acceleration. NVIDIA's 2:4 sparse Tensor Core is a representative hardware unit for N:M sparsity, capable of achieving up to  $2\times$  computational acceleration. Channel-wise sparsity aims to prune entire channels in a matrix, significantly reducing computation and storage needs. Table 4 shows the usage of three sparsity methods across different hardware platforms.

| Hardware | Weight Sparsity | Activation Sparsity | Attention Sparsity |

|----------|-----------------|---------------------|--------------------|

| CPU      | Х               | ✓                   | Х                  |

| GPU      | ✓               | Х                   | ✓                  |

| FPGA     | Х               | Х                   | X                  |

| ASIC     | Х               | X                   | ✓                  |

| PIM/NDP  | Х               | X                   | X                  |

Table 4: Sparsity on CPU, GPU, FPGA, ASIC, and PIM/NDP

## 3.2.2 CPU

Activation Sparsity. Activation sparsity is determined by activation functions. Commonly using SwiGLU [215] and GeGLU [216] exhibits limited sparsity for LLMs, but simply replacing these functions with ReLU fails to achieve sufficient sparsity. Turbo Sparse [130] proposes the dReLU activation function to improve LLM activation sparsity, along with a high-quality training data mixture ratio to facilitate effective sparsity. By applying their sparsity method to the Mistral and Mixtral models, only 2.5 billion (35.7%) and 4.3 billion (9.2%) parameters are activated per inference iteration, respectively. For Mistral-7B, Turbo Sparse achieves 8.71 tokens/s and 9.94 tokens/s on Intel i9-14900HX processor and Intel i7-12700K processor, respectively. For Mixtral-47B with 4-bit quantization, Turbo Sparse achieves 16.1 tokens/s, 11.98 tokens/s and 11.1 tokens/s on Intel i9-14900HX, Intel i7-12700K and SnapDragon 8 Gen3, respectively. ProSparse [131] also introduces activation function substitution, progressive sparsity regularization, and activation threshold shifting to help non-ReLU LLMs obtain high activation sparsity without performance degradation. For Llama2-7B and Llama2-13B, ProSparse achieves high sparsity of 89.32% and 88.80%, and 16.3 tokens/s and 8.67 tokens/s, respectively, based on PowerInfer [195] framework.

## 3.2.3 **GPU**

Weight Sparsity. LLM-pruner [132], adopts structural pruning that selectively removes non-critical coupled structures based on gradient information, maximally preserving the majority of the LLM's functionality. To this end, the performance of pruned models can be efficiently recovered through tuning techniques, LoRA, in merely 3 hours, requiring only 50K data. We validate the LLM-Pruner on three LLMs, including Llama, Vicuna, and ChatGLM, and demonstrate that the compressed models still exhibit satisfactory capabilities in zero-shot classification and generation.

LLMs can be pruned to at least 50% sparsity in one-shot, without any retraining, at minimal loss of accuracy. SparseGPT [133] requires a sophisticated weight update procedure in an iterative pruning process. Wanda [134] prunes weights with the smallest magnitudes multiplied by the corresponding input activations, on a per-output basis. Notably, Wanda requires no retraining or weight update, where pruning process is faster. Besides unstructured pattern, these two methods generalizes to semi-structured N:M (2:4 and 4:8) patterns. E-Sparse [135] introduces entropy to quantify the information richness within each channel (intra-channel) of the input features, and adopts it to enhance the feature norms (crosschannel) as a metric to evaluate parameter importance. Furthermore, it proposes Channel Shuffle to reorder the information distribution in LLMs to obtain N:M Sparsity with less information loss. 2:4 sparsity as supported by NVIDIA GPUs of generation Ampere and newer theoretically offers  $2\times$  acceleration of matrix multiplications. In practical, 2:4 sparsity can achieve  $1.54\times-1.79\times$  speedup for MatMul, and end-to-end speedups are about  $1.21\times-1.25\times$  (due to some extra overheads from e.g. attention).

Based on the key observation that the bottleneck of LLM inference is the skinny matrix multiplications, Flash-LLM [136] proposes a general Load-as-Sparse and Compute-as-Dense methodology for unstructured sparse matrix multiplication. Flash-LLM proposes a new sparse format called Tiled-CSL to relieve the memory bandwidth bottleneck and support the tile-by-tile SpMM execution with tensor cores. For OPT-30B, Flash-LLM achieves 80% sparsity with 1.44% accuracy decrease and about 290 tokens/s, 500 tokens/s, 800 tokens/s, and 1187 tokens/s on single A100 GPU with batch sizes 8, 16, 32, and 64, respectively.

Agarwalla et al. [137] combine the SparseGPT one-shot pruning method and sparse pretraining to pretrain a high sparsity LLM. They deploy model on GPU and CPU by utilizing Neural Magic's DeepSparse engine and Neural Magic's nm-vllm engine, respectively. For Llama-7B, on NVIDIA A10 GPU, they achieve 44.4 tokens/s and 47.9 tokens/s with 50% sparsity and 70% sparsity, respectively. On AMD EPYC 9R14 Processor, they achieve 4.4 tokens/s and 6.9 tokens/s with 50% sparsity and 70% sparsity, respectively.

Existing methods require costly retraining, forgo LLM's in-context learning ability, or do not yield wall-clock time speedup on modern hardware. DejaVu [138] predicts contextual sparsity on the fly given inputs to each layer, along with an asynchronous and hardware-aware implementation that speeds up LLM inference. For OPT-175B model, DejaVu achieves up to 75% sparsity and 50 tokens/s on 8 A100-80GB GPUs with batch size 1, which is over  $2 \times$  and  $6 \times$  faster than FasterTransformer and Hugging Face implementation, respectively.

**Attention Sparsity.** During the prefilling phase of LLM inference, attention computation complexity scales quadratically with input sequence length. Given limited GPU computing and memory resources, attention sparsification can reduce the number of attention values to accelerate prefilling phase. For static sparsity, Sparse Transformer [139], StreamingLLM [141], Bigbird [140], and Longformer [142] use the manual combination of global and local patterns to replace the full attention patterns. The local pattern captures the local context of each token within a fixed size or stride while the global pattern captures the relationship between the specific tokens to all other tokens. For Llama2-7B and Llama2-13B models, StreamingLLM achieves 15.38-32.26 tokens/s and 9.43-20.83 tokens/s on single NVIDIA A6000 GPU, respectively. For dynamic sparsity, Adaptively Sparse Attention [143] replaces softmax with  $\alpha$ -entmax, a differentiable generalization of softmax that allows low-scoring words to receive precisely zero weight and drops parts of the context that are no longer required for future generation. Reformer [144] replaces dot-product attention by using locality-sensitive hashing, changing the complexity from  $O(L^2)$  to O(LloqL), where L is the sequence length. Sparse Flash Attention [145] extends FlashAttention [217] GPU kernel and encompasses key/query dropping and hashing-based attention. Sparse Sinkhorn Attention [146] adopts a learned sorting network to align keys with their relevant query buckets, ensuring that attention is computed only between the corresponding query-key pairs. H<sub>2</sub>O [147] observes that a small portion of tokens (called Heavy Hitters, H<sub>2</sub>) contributes most of the value when computing attention scores. H<sub>2</sub>O introduces a dynamic attention sparsification method to adopt KV cache eviction policy that dynamically retains a balance of recent and H<sub>2</sub> tokens. For OPT-6.7B model, H<sub>2</sub>O with 20% H<sub>2</sub> achieves 30.4 tokens/s on single NVIDIA T4 GPU.

## 3.2.4 FPGA

Weight Sparsity. FlightLLM [120] is the first real FPGA-based LLM accelerator which proposes a configurable sparse DSP chain to support different sparsity patterns with high computation efficiency. Then, it proposes an always-